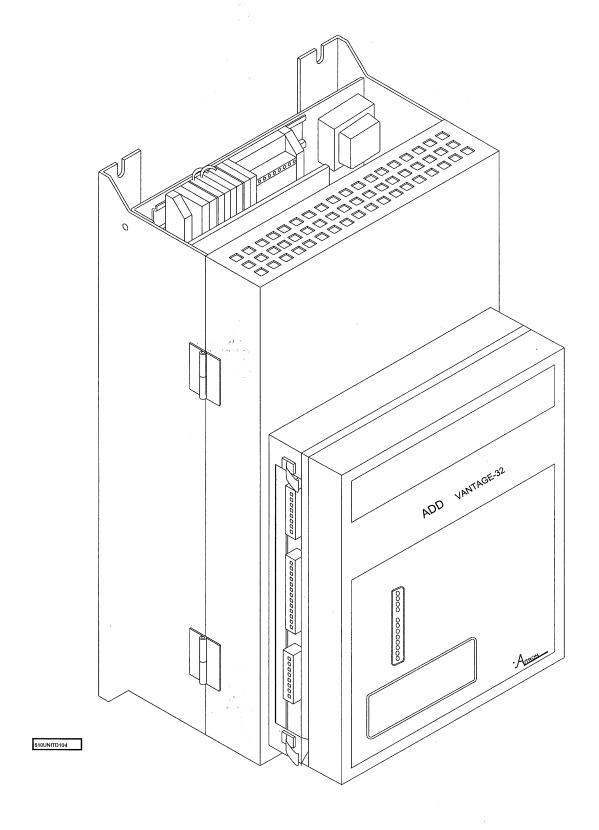

### AVTRON ADDvantage-32 AC TO DC POWER CONVERTER ADVANCED FIELD SUPPLY CONTROLLER

|  | ······································ |   |     |   |

|--|----------------------------------------|---|-----|---|

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     | • |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  | •                                      |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        | • |     |   |

|  |                                        |   | · · |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

|  |                                        |   |     |   |

# AVTRON ADDvantage-32 AC TO DC POWER CONVERTER ADVANCED FIELD SUPPLY CONTROLLER

#### **DIFFERENCE DATA**

The Advanced Field Supply Controller (AFS) is the same as the DMG (Digital Motor/Generator Set Controller) described in this manual except for the following:

#### **DESCRIPTION**

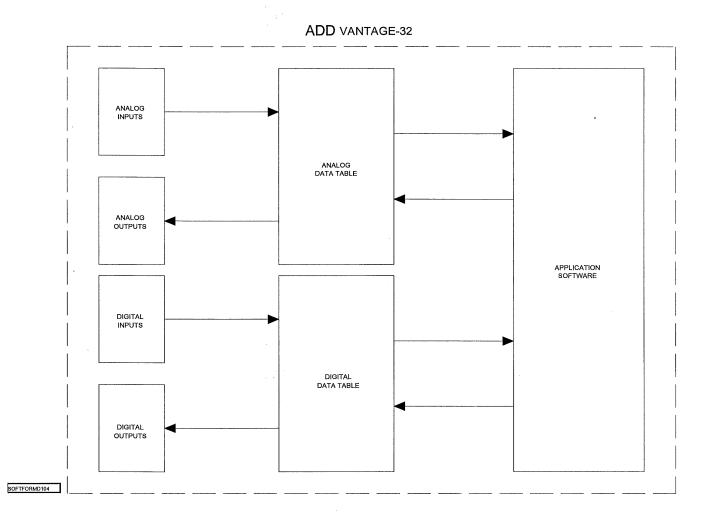

The Avtron AFS converts AC power into DC for DC motor shunt fields. The hardware includes a full wave, 3-phase rectifying bridge. AFS Controllers are available from 10 amps to 510 amps. AFS software provides control for the fields.

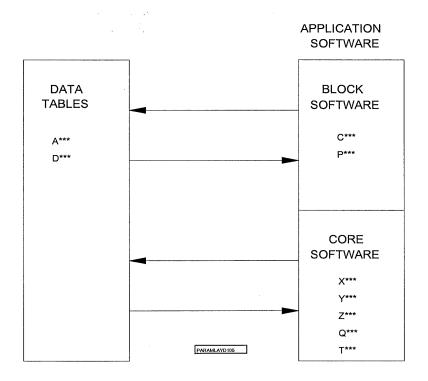

The AFS software is segmented into two parts. The first part is the application blocks. These allow the user to set up the AFS to control a fixed field, CEMF control, load share or speed control. Protection blocks can be configured to user faults to protect the motor from field loss, field control loss and over/under voltages. See the appendices for block descriptions and setup.

The second part of the software is the base code. This code controls the I/O, faults, communications, keyboard, lower level current regulators and bridge firing. This software was taken from the Avtron DMG regulator (motor generator controller). Both regulators share the same base software. The advantage of doing this ensures that future revisions are done to both field controllers.

#### **DRAWING PACKAGE**

In addition to the attached DMG manual, a separate drawing package is supplied that covers specific hardware part numbers. Information in this drawing package supersedes any corresponding information in the DMG manual. Specifically, IDENTIFICATION OF PART NUMBERS in Section I of this DMG manual only pertains to a DMG part number. Refer to the separate drawing package for AFS part number description. Along with any required drawings, the drawing package also supplies a list of the drawings, a list of recommended spare parts, and replacement parts information.

|   |   |   | • |

|---|---|---|---|

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

| 1 |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   | , |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   | 4 | • |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

#### **DIFFERENCES**

The two controllers are identical except for the following two items:

The DMG has a main field supply and an auxiliary field supply. The AFS only has the main field supply.

The DMG has an interposing contactor relay. The AFS has no contactor output.

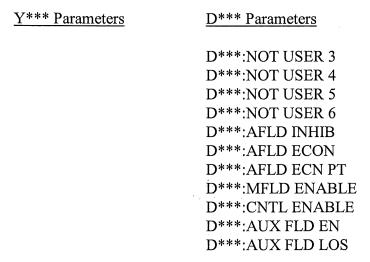

The base software has parameters to set up both the auxiliary field and motor contactor, which the AFS does not use. The base parameters that are described as main field are applicable for both regulators. The parameters that are described as the auxiliary field apply to the DMG only. These include the following:

Xxxx:MTR I AFLD

Xxxx:AFLD %SCALE

Xxxx:AFLD ASCALE

Xxxx:Max AFLD A

Xxxx:Min AFLD A

Xxxx:AFLD Resist

Xxxx:AFLD Tx Rat

Xxxx:AFLD LOSS

Xxxx:AFLD PHASE

Xxxx:AFLD PGAIN

Xxxx:AFLD IGAIN

Yxxx:AFLD B-TYPE

Yxxx:AFLD V-CMD

The contactor logic is present in both and can be used by the AFS to close a user digital output if desired.

#### **OTHER SOFTWARE DIFFERENCES**

The DMG has parameters to configure armature current feedback. This is used in the base for IIR overload and in the application for the armature current loop. For the AFS, this setup is not required but can be used. The parameters to set this up are:

Xxxx:MOTOR Iarm Yxxx:IARM FBK PT Yxxx:IIT FAULT

|  |  |   |   |   |  | * |

|--|--|---|---|---|--|---|

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  | • |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   | * | • |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

|  |  |   |   |   |  |   |

The auxiliary field supply needs to be disabled in the AFS since it does not exist. If this is not disabled, the controller may trip out on auxiliary field loss. This is done be setting Yxxx:AFLD CNTL = Disabled.

The Field economy switch affects the auxiliary field in the DMG. In the AFS it affects the main field. This is set by parameter Yxxx:AFLD ECN SE.

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

| e<br>Le<br>L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

| Control of the Contro |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |  |  |